EkThaTiger

Active Member

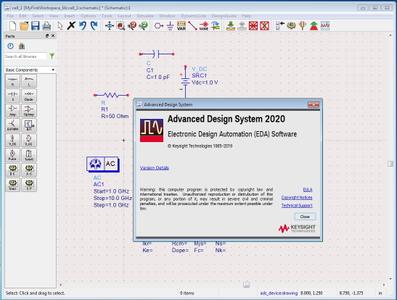

Keysight Advanced Design System ADS 2020.0

File Size: 2.02 GiB

Keysight Technologies Inc. has announces the availability of Advanced Design System (ADS) 2020.0. This release added new RFPro features, FEM perf., new Winslow stability analysis, new/improved PCB vias/padstacks, data file mgmt., expression mgr. and Data Display perf., Electro-Thermal enhancements, new PDK validator, new SI/PI, DDR/SerDes features, new PEPro.

Advanced Design System (ADS) 2020.0 Release notes - Date: 2019-07-26

Design and Technology Management

General

- Improved Reference Searching and Display. "Explain" references describes and shows reference information to explain relationships in your libraries and designs.

- Improved Data file support in Library View and Copy Files.

Data Display

- Added Data Display Expression Manager to edit, find and/or replace equations and export measurement equations.

- Find equation and trace dependents in Data Display.

- Data Display Performance Improvements.

Datalink (Python Interface)

- Datalink functions are available in measurement equations.

Design Editing

- Layout Constraints Database is a central location to define constraints on layout designs, such as trace widths, via start and stop layers, and routing clearances. The initial release of the layout constraints database implements two types of constraints: Clearance constraints and Via constraints.

- Define and Insert PCB Vias and Pads using Padstack Templates.

Circuit Simulation

General

- Loop Gain based stability analysis.

- Support SystemVue 2018 update1.0 and latest 5GNR for modulated signals.

- Direct EVM computations without dataflow simulator.

- Simulated annealing optimization supports discrete variables and has improved performance.

Electrothermal

- Using Design with Non-Synchronized Hierarchy.

- Electrothermal controller default values can be pre-configured using the eth.cfg file.

- Beta - ETH Circuit Envelope simulation allows the specification of an arbitrary synchronization time schedule (that is arbitrary time steps as a function of time) in contrast to the preceding uniform or logarithmic progressions.

- For more details on use of arbitrary timestep, see Parameters in Simulator timestep Section.

NXP SiMKit Models

- The models have been updated to SiMKit Release, and these are now the default.

- For more information, including supported device versions, see Devices and Models, NXP SiMKit.

HSD Design

General

- Queue Manager (QM) to manage test bench/benchs in ADS.

SerDes

- CTLE Visualizer. For more information, see CTLE Equalization Parameters.

. Easier CTLE setup with provided presets for OIF CEI-28G. CEI-56G-VSR, IEEE 802.2bs CDAUI8, PCIe and USB Gen3.

. Display frequency response, magnitude and phase.

. Support user provided presets.

- MIPI C-PHY Receiver enhancement with CTLE.

- FlexDCA_Probe connection enhancement for remote H/W and remote PC.

- COM (Channel Operating Margin).

. Linux Matlab runtime support.

. COM 2.6 and Matlab R2018b support.

- Smart Eye Probe: Multilane support with triggered eye diagram.

DDR/Memory

- DDRSetup for Memory Designer

. Improvements in setup SIPro simulations for DDR design

. Improvements in use flow SIPro->Memory Designer

- DDR Package components to specify packages that are not part of an IBIS file.

EM-SI/EM-PI

- Via Designer

. multi-feed vias

. micro vias and staggered vias

. export to layout

. export to EMPro

. custom stitching via layers

- Parallel simulation jobs for SIPro

. local parallel simulations

. parallel simulation jobs on cluster

- Component Model Maker

. PCB Import generates a Model Map File

. Model Map File generates Schematics and Symbols for user selected components

. Model Map File can be edited to point to vendor libraries and custom models

- PIPro DeCap Optimization with Lib Cell and SnP Components

- PIPro Multi-Pin Splitting from 1 Sink to Multiple Sink Pin Pairs

- PIPro Multi-Pin Accuracy Improvements

. Equal Current and Equal Voltage now result in lower impedance with improved distribution of currents.

- ADFI Export for Package Import into PIPro

. Custom ADFI setting for exporting packages from Cadence SiP and MCM for use in SIPro/PIPro.

- PIPro Improved multi-pin grouping and ungrouping for Current Mode and Voltage Mode AC EM Model solutions.

- Faster rendering of large designs during rotate/pan/zoom. During these operations, reduced geometry detail is rendered to preserve an acceptable frame rate.

EM Simulation

RFPro

- The User-Defined EM Extraction analysis allows to EM-simulate a combination of selected nets and components of a large design.

- Simulate frequencies in parallel with FEM (on the local host or submitted to a cluster queue) and Momentum (only supported for jobs submitted to a cluster queue). Specify the number of parallel jobs in the Analysis → Options → Resources tab.

- LTD substrate files are available for selection when creating a new RFPro view.

- Specify the layer purposes to be excluded or included when opening a layout in RFPro in the substrate editor (.subst or .ltd).

- Context menus have been added to pin(s) allowing to create a virtual pin on a layer.

- The S-Parameter → Save As dialog has a new flag to open a Data Display window after exporting the S-parameters to a dataset.

- Create Script context menu option has been added to analyses allowing you to transfer an analysis setup to another view. The script can also serve as a starting point for learning how to define an analysis through a python script.

- Faster rendering of large designs during rotate/pan/zoom. During these operations, a reduced geometry detail is rendered to preserve an acceptable frame rate.

- Preview the next generation FEM simulator by setting the environment variable RFPRO_FEM_GENERATION=2. The 'pilot' code in the ADS 2020 release brings much faster pre-processing of (multi-technology) designs and a 'Mesh Domain Optimization' simulator option. The new flow can be used as an alternative to the default (RFPRO_FEM_GENERATION=1) FEM simulator.

- ADS 2020 release is the last release with Python 2.7 as Python 2.7 is reaching its end-of-life. ADS 2021 release is planned to use Python 3.7. A pilot release with Python 3.7 is available for download. Contact Technical Support for further guidance.

- ADS 2020 release is the last release to support 32 bits version of Cadence Virtuoso. ADS 2021 is planned to support only the 64 bits versions of Cadence Virtuoso.

EM Setup

- An issue has been addressed in the EM Setup based interoperable EM-Cosimulation flow. The view generation failed when 1x1 OA via arrays are present in the layout.

FEM

- Mesh generation performance and robustness improvements.

- Increased robustness of the parallel frequency sweep.

- Queue resource mapping tied to master/mesh/solve phase with 'sitecluster'.

Momentum

- Refinement of the AC-behavior of the new conductor loss model introduced in ADS 2019. When cumulating edge mesh and thick metals, it could lead to an overestimation of the resistance with increasing frequency. This issue has been addressed. The workaround of setting MOM3D_USE_LOCALTHICKNESS = 0 is no longer recommended.

Power Electronics

Power Electronics Professional (PEPro)

- Next generation post-layout EM-circuit co-simulation platform for switched-mode power supply (SMPS) designs.

- Automatic optimum settings of EM and Transient/Convolution simulation controllers for SMPS design.

- Pre-built testbenches for Voltage Spikes and Conducted EMI analyses.

PDK Validator

Process Design Kit (PDK) Validator provides automation technology for delivering high quality, fully enabled ADS PDKs.

- Verify PDKs with a new ADS release

- Enable features (DRC, LVS)

Design Rule Check (DRC)

Assura DRC

Rule Categories

- Improved support for rule files with switches. Switches are now automatically detected.

ADS DRC

Capacity and Performance

- Improved support for large rule files with many input layers.

- Improved efficiency for the dve_quadout() command

. Impacts rules that perform an external clearance rule and then extract quadrilaterals from the selected edges. Can result in a significant performance improvement for designs that contain circles or traces with round end type.

DRC Documentation

- 100+ examples of how to write rules.

- Find information easily. Browse to the Rules using the Navigation panel.

- Writing Design Rules provides sample rules files that illustrate rule categories and process variants.

Rules syntax updated to show all supported parameters. For example, Polygon Selection rules support a message parameter which provides a simpler rules syntax.

Design Kits

- Updated the Si-RFIC PDK Model Include Utility for the following:

. "None" scenario has been added as one of the default scenarios.

. Updated the Model Include Component, you can now invoke the settings dialog box from the component itself.

- For more information, see Si RFIC PDK Model Include Utility.

- Removed the following legacy and old ADS demo kits from ADS 2020 installer:

. DemoKit

. DemoKit_V3

. SampleKit

. eesofDemoKit

- You can download the above listed design kits from the Knowledge Centre for legacy purposes only. Any training modules using these old kits need to be updated with the latest ADS Non-Linear Demo Kit.

- Updated the ADS Non-Linear Demo Kit for the following:

. All the DSN references have been removed from the design kit.

. A new substrate "demo_modified.subst" is added with practical values of material conductivities to synthesize more realistic inductors.

. CNEX Component Definitions are added to support Calibre LVS and Assura LVS.

Verification Test Bench (VTB)

- The Single Port VTB (only Source) simulation is now supported. Now, you can create complex modulated sources in SystemVue and use with ADS Circuit Envelope.

- From ADS 2017, to install files that are required for the VTB functionality you need to download a separate VTB installer (for Windows only). For Linux, the VTB installer is bundled with ADS installer.

. It is recommended to download compatible ADS and VTB installers to the same directory. After the download, run the ADS installer. This process will automatically install the VTB functionality.

. If you have already installed ADS and find VTB functionality is missing, then you need to download and install the VTB.

- Upgraded SystemVue 2018 engine in ADS.

. Added the following new VTBs:

.. 5G Advanced Modem Workspaces

.. NB IoT Workspaces

. Updated the name of the existing VTBs:

.. WLAN 11ac Workspaces

- ADS 2019 only supports import of Custom VTB (SystemVue workspace) created using SystemVue 2018 and SystemVue 2018 Update 0.1.

Examples

- All the newly added examples are searchable using the Example Search dialog box.

Documentation

- Starting with the 2020 release, the online help gets a new user interface. The new UI improves overall online help usability by providing the following key benefits in addition to several other minor benefits:

. Table of Contents Sidebar: Displays collapsible Table of Contents for the entire documentation. The left-double-arrow icon collapses the sidebar, and the right-double-arrow icon displays the sidebar back again.

. PDF Button: Allows you to instantly generate PDFs of the latest documentation anytime, including current page's children pages. Currently, the PDF generation option is available only for ADS 2020 release. For other releases, you can switch to their Printing Manuals page and download the existing PDFs like earlier. Note that with the introduction of PDF generation feature, the Printing Manuals page will not be available from next release onward.

. Product Release Switcher: Allows you to view the current page in other supported releases listed in the drop-down menu. Once you select a release from the drop-down menu, the current page is updated to show the content applicable to the selected release. The Table of Contents is updated as well. With this, you bookmark URL of only one release and then switch to other releases from this drop-down menu.

. Latest Documentation: The documentation available in the new UI is always kept updated for all supported releases. These updates are available to you as soon as they happen at our end. This provides you 24x7 access to the most recent and technically accurate documentation.

Advanced Design System (ADS) is the world's leading electronic design automation software for RF, microwave, and high-speed digital applications. ADS pioneers the most innovative and powerful integrated circuit-3DEM-thermal simulation technologies used by leading companies in the wireless, high-speed networking, defense-aerospace, automotive and alternative energy industries. For 5G, IoT, multi-gigabit data link, radar, satellite and high-speed switched mode power supply designs, ADS provides an integrated simulation and verification environment to design high-performance hardware compliant with the latest wireless, high speed digital and military standards.

This video shows you how to use basic signal integrity (SI) analysis techniques such as eye diagrams, S-parameters, time-domain reflectometry (TDR) and single pulse response to solve signal integrity problems.

Keysight Technologies Inc. is the world's leading electronic measurement company, transforming today's measurement experience through innovations in wireless, modular, and software solutions. With its HP and Agilent legacy, Keysight delivers solutions in wireless communications, aerospace and defense and semiconductor markets with world-class platforms, software and consistent measurement science. The company's nearly 10,500 employees serve customers in more than 100 countries.

Product: Keysight Advanced Design System (ADS)

Version: 2020.0

Supported Architectures: x64

Language: English

System Requirements: PC *

Supported Operating Systems: *

Size: 2.1 GB

System Requirements:

Recommended

RAM: 32 GB RAM or higher

Hard Disk Space: 512 GB free disk space or greater

Processor: 64-bit, multi-core CPU

Screen Resolution: 1080p (1920x1080) or 4k (3840x2160) display resolution with true color

Model Development dependency for model development: Visual Studio 2017

Minimum

RAM: 8 GB RAM or higher

Hard Disk Space: 20 GB free disk space or greater

Processor: 64-bit CPU

Screen Resolution: 1024x768 display resolution with true color

Model Development dependency for model development: Visual Studio 2017

Operating System

- Windows 7 Enterprise (64-bit)

- Windows 10 Enterprise (64-bit)